sigrity 2021全称为cadence sigrity 2021或Cadence Design Systems Analysis Sigrity 2021,由美国Cadence公司推出的一款PCB电路设计仿真软件。软件带来了多项新的仿真功能,专为加速PCB电源完整性及信号完整性仿真流程量身打造。采用分析模型库管理器,实现对电源完整性模型内容库的管理,所有模型皆可实现自动存储并在复用设计组件时从分析模型管理器内容库中取回。大大地降低了企业开发的成本,同时还集合了最新的PCIe技术,能够有效地保证信号的完整性。

与之前版本相比,全新的sigrity 2021带来了许多新的升级和优化,提供了场解算器,如Sigrity的PowerSI软硬结合支持技术,可实现的是通过从刚性PCB材料以柔性材料高速信号的鲁棒分析。全新的3D Workbench解决方案弥补了机械和电气领域之间的隔阂,产品开发团队自此能够实现跨多板信号的快速精准分析。设计团队现在可以使用以前仅用于刚性PCB设计的相同技术,从而在PCB制造和材料工艺不断发展的同时实现分析实践的连续性,能够采用更全面的方法进行产品优化,不仅包括芯片,封装和电路板,还包括机械结构,集合了最新的PCIe技术,能够有效地保证信号的完整性。

PS.本站为你提供的是cadence sigrity 2021.1破解版,

此版本内置破解补丁可以完美激活软件,后文提供详细的安装教程,有需要用户欢迎下载体验。

sigrity 2021破解版安装教程

0、

如果安装有旧版本,先将其卸载删除;

1、解压镜像,得到sigrity 2021破解补丁和安装程序;

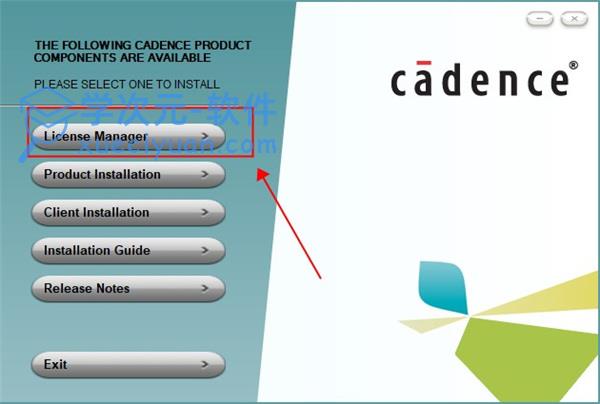

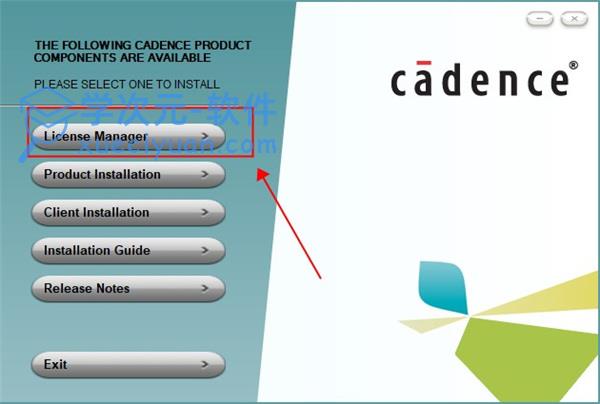

2、运行setup,安装“Cadence License Manager”,并关闭“Cadence许可证服务器配置”窗口

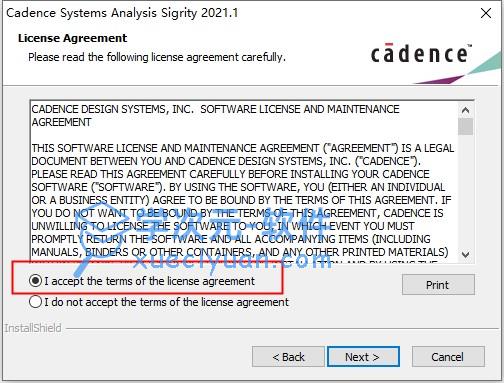

3、点击"Product Installation" ,安装Cadence Design Systems Sigrity;

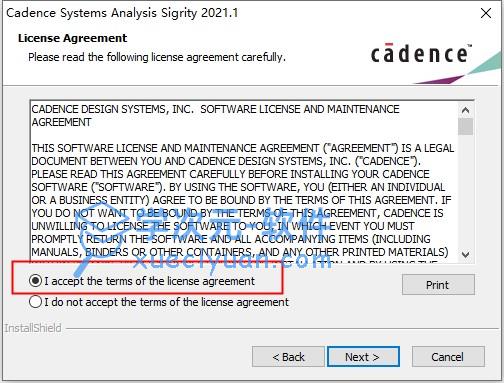

4、接受同意许可条款,然后下一步安装;

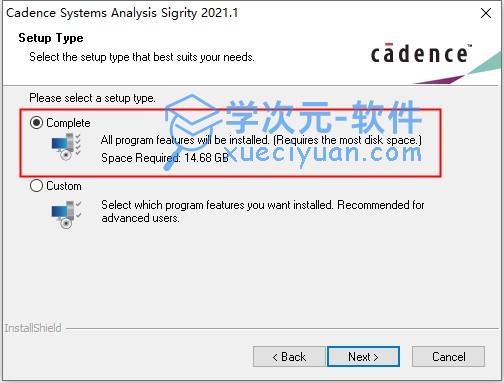

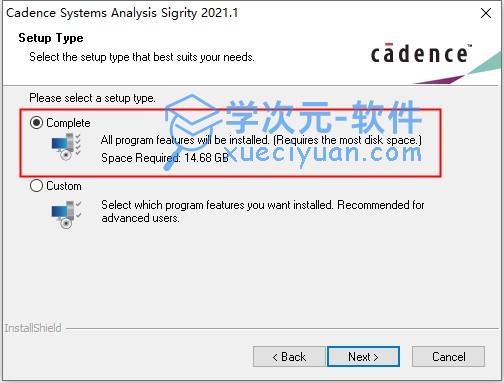

5、使用默认设置安装应用程序,等待安装完成即可;

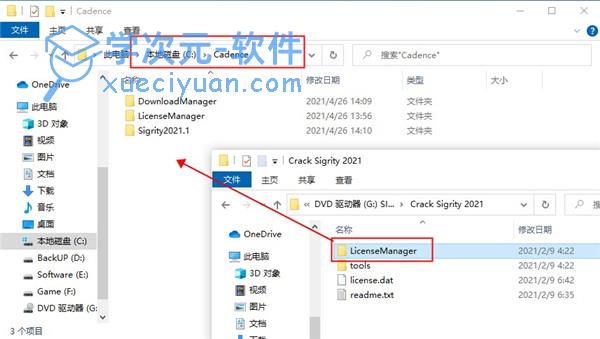

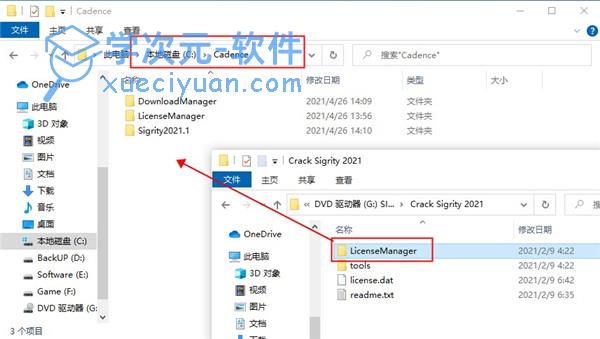

6、复制破解文件夹下的LicenseManager至:C:\Cadence\,并运行LicenseManagerPubKey.bat;

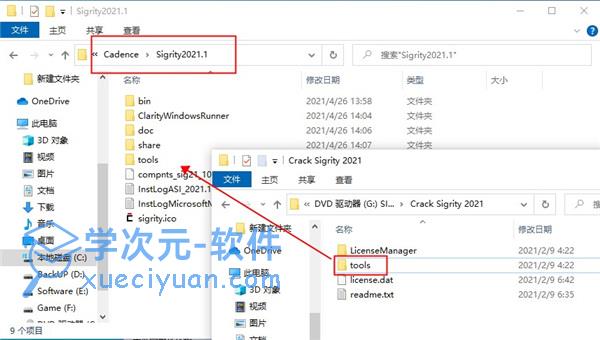

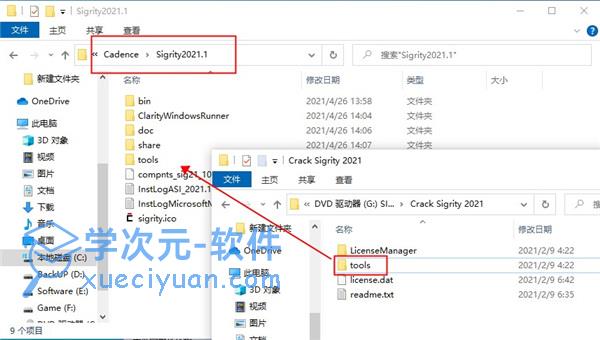

7、复制破解文件夹下的Tools至:C:\Cadence\Sigrity2021.1,并运行并运行“ToolsPubKey.bat;

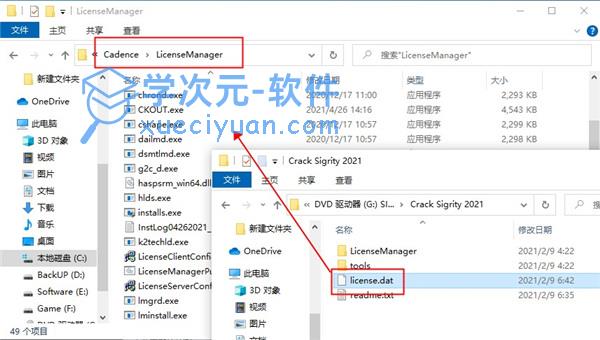

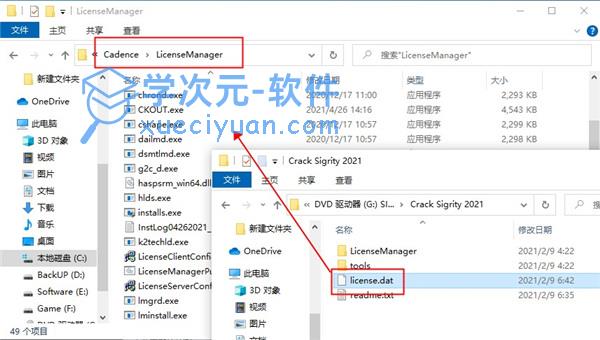

8、复License.dat至:C:\Cadence\LicenseManager;

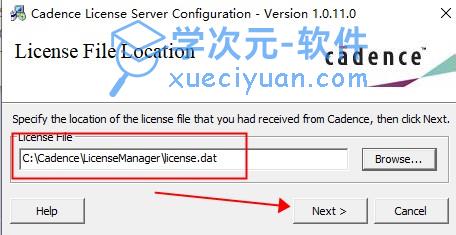

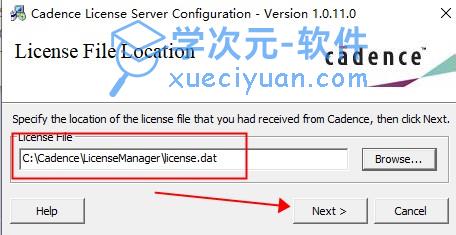

9、在C:\Cadence\LicenseManager中打开LicenseServerConfiguration.exe,浏览添加License.dat;

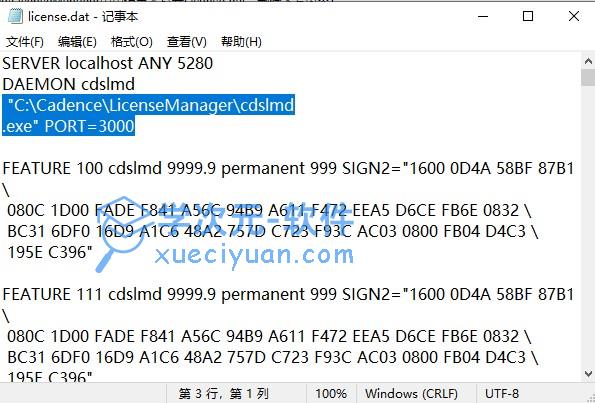

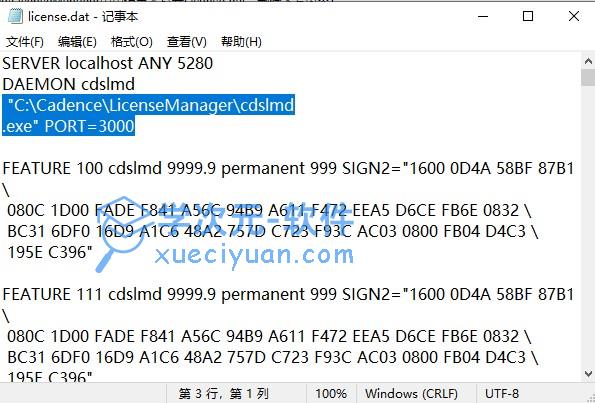

10、在C:\Cadence\LicenseManager中用记事本打开License.dat,删除下方内容:

"C:\Cadence\SPB_17.2\LicenseManager\cdslmd .exe" PORT=3000

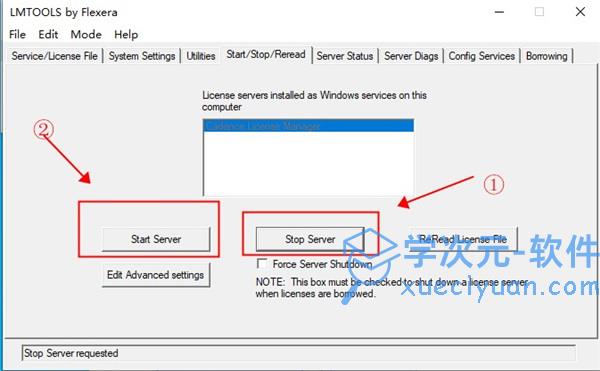

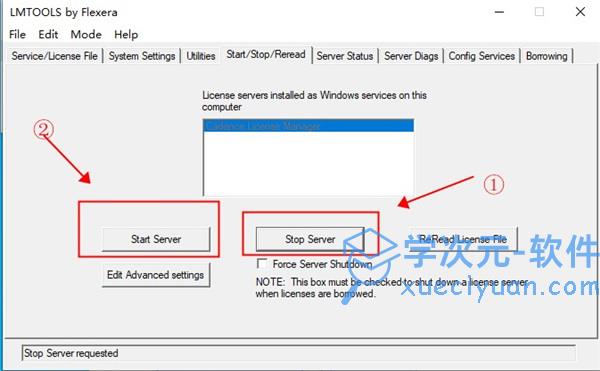

11、在C:\Cadence\LicenseManager中打开lmtools.exe,选择"Start/Stop/Reread"选项卡,先点击"Stop Server"再点击"Start Server";

12、至此,cadence sigrity 2021.1破解版完成安装,希望以上教程对你有所帮助;

软件特色

1、互连建模技术。

升级的互连建模技术满足了PCB和IC封装设计的最新趋势。随着信号速度攀升至32Gbps或更快,现在需要将PCB和连接器作为一种结构进行战略建模。

2、3D工作台提供。

SI和PI应用程序、熟悉的3D外观、能够导入机械结构、-能够导入电气数据库并与机械结构合并、3D实体建模(参数化和全功能)。

模拟:Twisted对布线(电缆)、板加连接器、连接器建模(HDMI,SATA等)、PCB上的SMA连接器。

3、刚性-柔性支持。

业界首例从单一布局数据库中提取完整的刚性-柔性PCB,可为刚性和网格接地柔性电缆区域提供准确的互连建模。区域信息是从CadenceAllegro技术的17.2版自动导入的。

4、更快的IC封装建模。

具有数千个焊球/焊球的设计的IC封装建模现在快了3倍,并且内存消耗降低了75%。

5、电源完整性更新。

升级的电源完整性(PI)技术可满足PCB前后设计流程的新检查要求和新可用性要求。添加了许多增强功能,包括分层视图,快速搜索和过滤,比较树报告以及工具提示。

6、Allegro PowerTree技术。

DC分析技术已升级,以支持与Allegro技术的集成,HTML框图的增强以及自动焊盘上添加节点的增强。

7、PowerDC技术。

交流分析技术增加了一些附加检查,现在可以检查加权的交流电流并检查是否相等电压。新的批处理模式“项目”允许将这两个新工作流程以及其他工作流程设置为一组批处理检查。

8、OptimizePI技术。

升级的信号完整性(SI)技术缩短了验证内存接口,串行链路以及PCB上过多其他信号的时间,这些信号可能导致设计在实验室中失败。该技术现在具有工作流程和视觉,可用于快速执行电气规则检查,以发现阻抗变化和过度耦合。这些检查不需要任何模型,并且可以由信号完整性方面的专家和非专家共同运行。

新功能

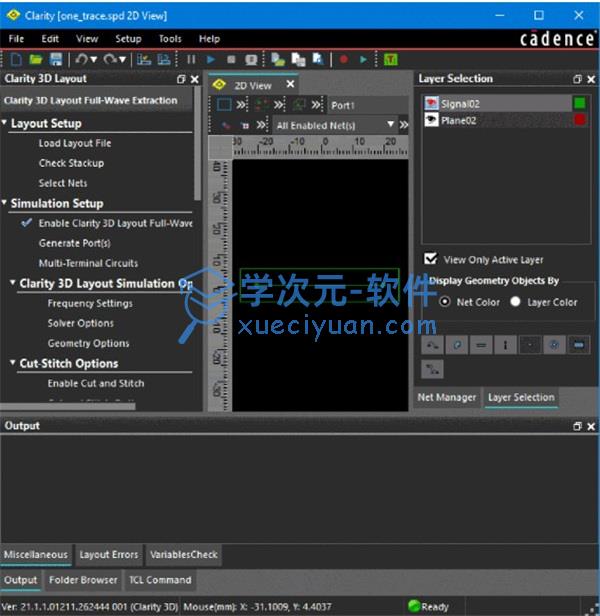

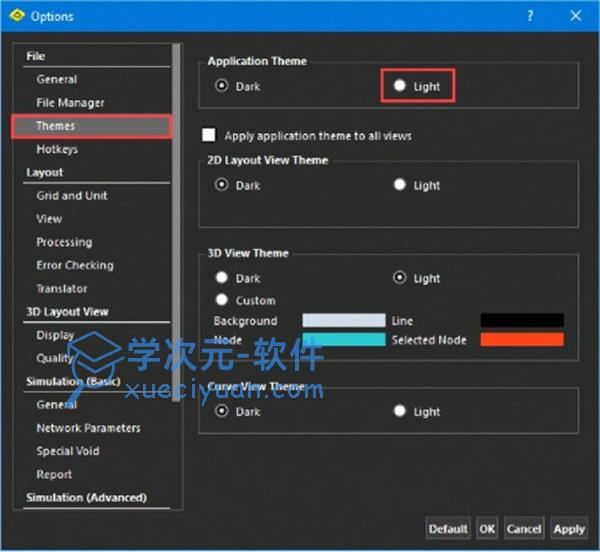

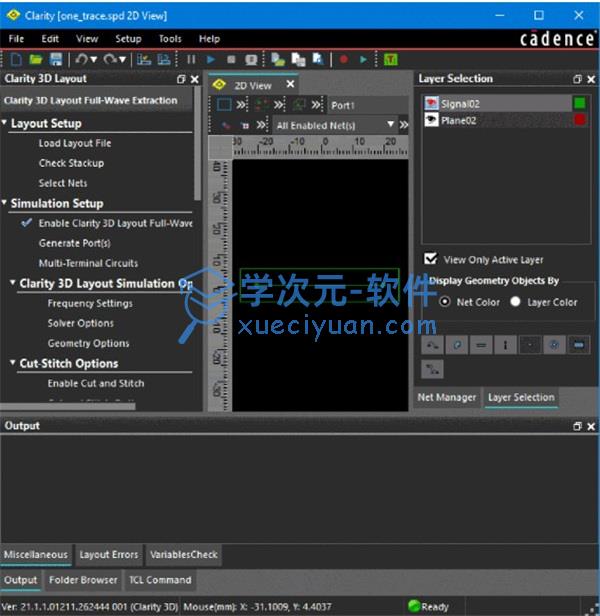

1、UI外观已更改

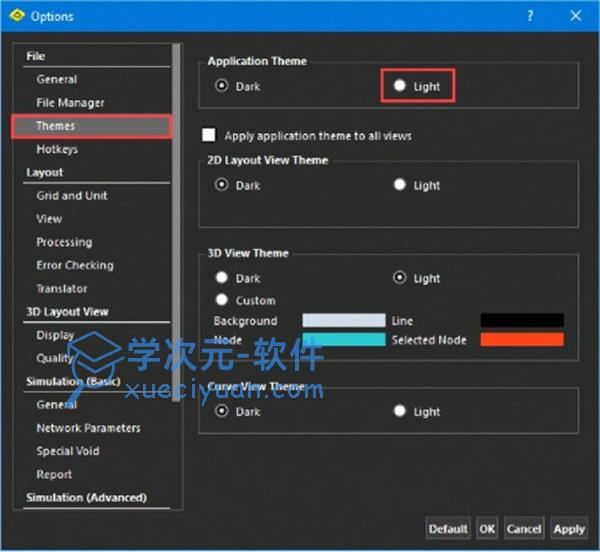

(新)在此版本中,Clarity 3D Layout的用户界面已更改。默认情况下,Clarity 3D Layout现在使用深色应用程序主题。

如果需要,可以通过单击“选项”页面上的“主题”选项卡并选择“灯光”选项来切换到灯光主题。

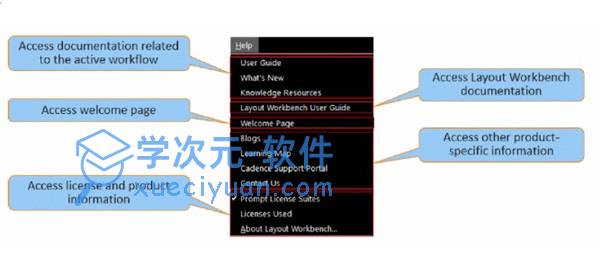

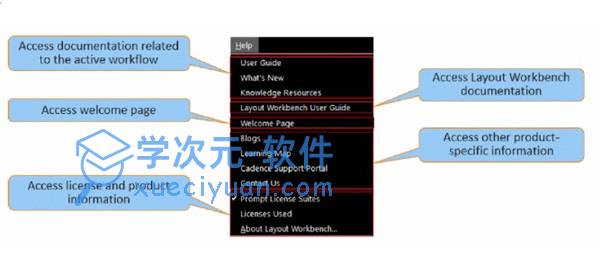

2、帮助菜单进行了改进

(新)已修改了使用Layout Workbench可以访问的所有工具的“帮助”菜单,包括Clarity 3D Layout。几个新选项已添加到“帮助”菜单中,使您可以从Cadence支持和公司网站访问最有用的帮助和支持资源。

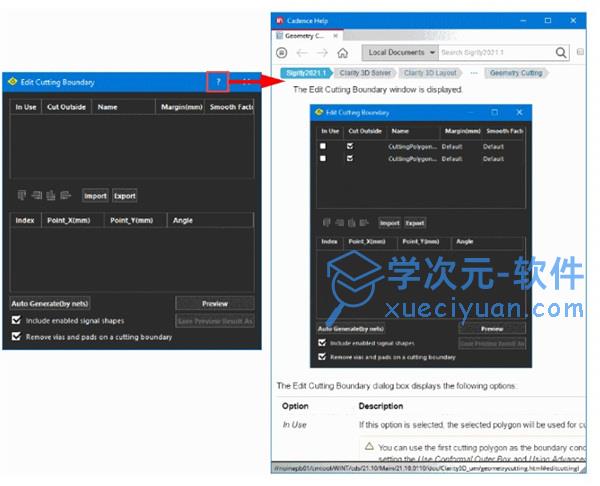

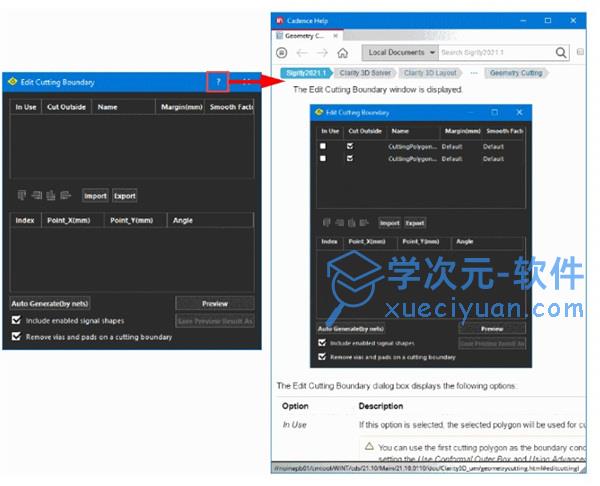

3、添加了上下文相关帮助来访问文档

(新)以问号(?)形式出现的帮助按钮已添加到多个工具中,包括Clarity 3D Layout。这些帮助按钮使您可以在Cadence帮助窗口中查看有关UI表单或功能的详细文档,如下所示。

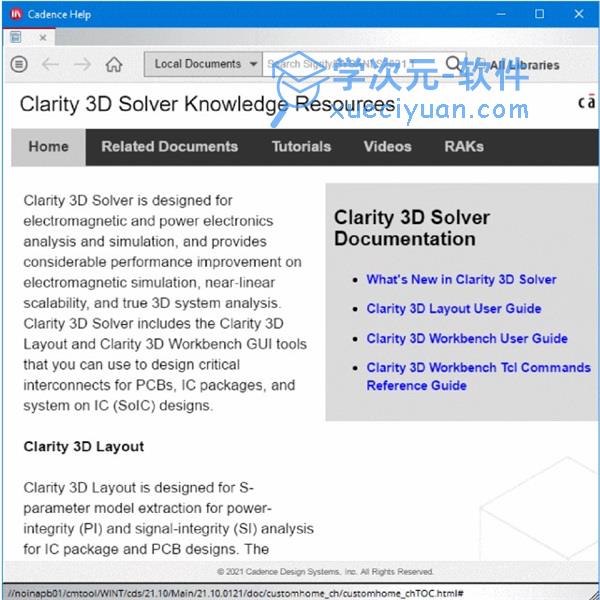

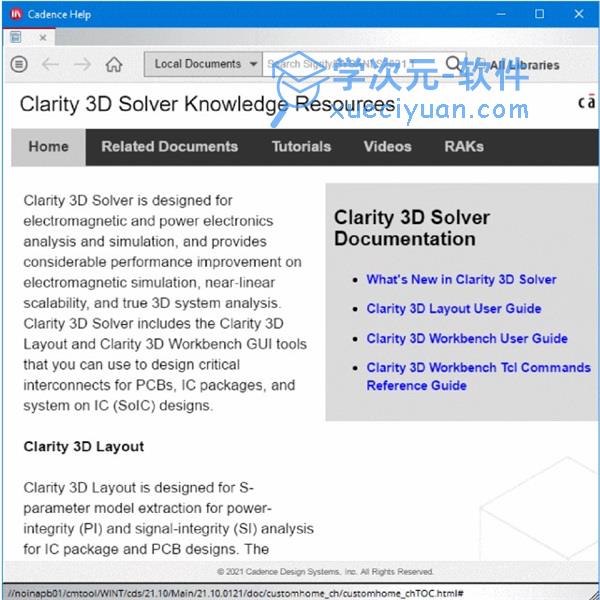

4、添加了新的知识资源页面

(新)已在多个工具(包括Clarity 3D Layout)中添加了新的知识资源网页。该页面通过整齐的选项卡式界面提供对各种有用的知识资料的访问,例如教程,视频,RAK和相关文档。

若要访问知识资源网页,请从“帮助”菜单中选择“知识资源”。

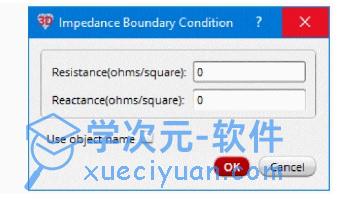

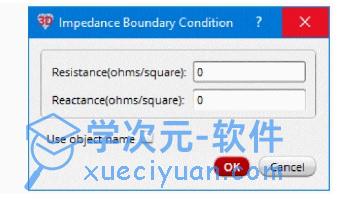

5、增加了对新边界条件的支持

(新)Clarity 3D Workbench现在支持以下新的边界条件:

阻抗边界–阻抗边界条件用于模拟电阻表面。 例如,如果结构由被薄膜电阻器隔开的两种介电材料组成,则该电阻器可以由两个对象之间的表面处的阻抗边界表示。

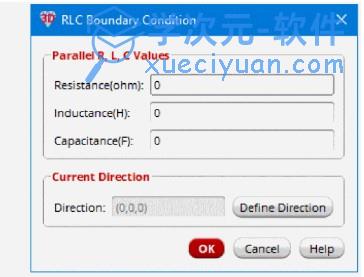

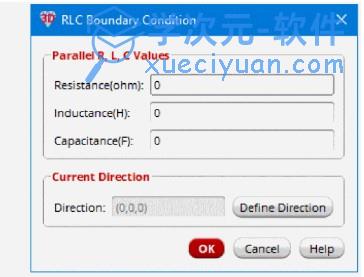

RLC边界– RLC边界条件用于建模集总电阻器,电感器和电容器。 您可以定义2D图纸并在其上应用RLC边界条件。 RLC边界条件通常表示为电阻,电感,电容的并联组合。 例如,要对电阻器建模,电感和电抗值应为0。

6、添加了几何修复选项

(新)将设计导入到Clarity 3D Workbench中时,某些导入面的质量可能不符合预期。 例如,几何图形可能有一些不良的面,或者钣金主体可能具有开放区域。 在早期版本中,Clarity 3D Workbench中没有可用的选项来处理这种情况。 在此版本中,添加了以下修复选项:

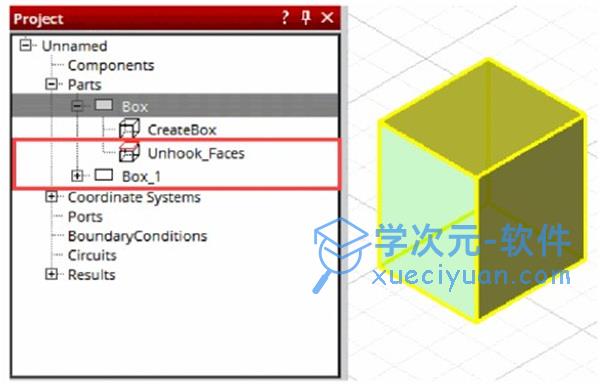

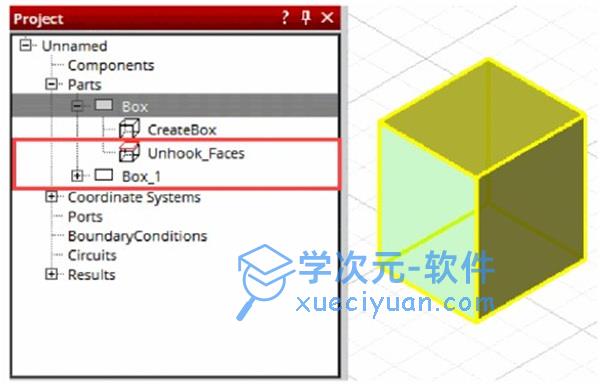

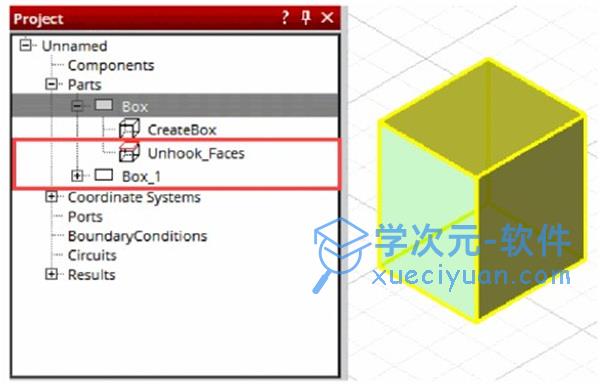

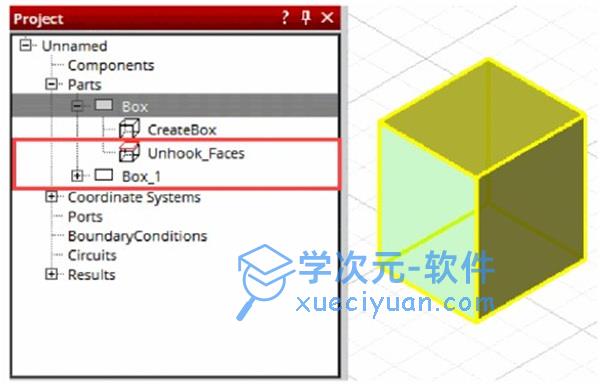

Unhook Faces-可以使用“建模器”菜单中的“模型清理-Unhook Faces”选项从几何图形中分离出不良面。

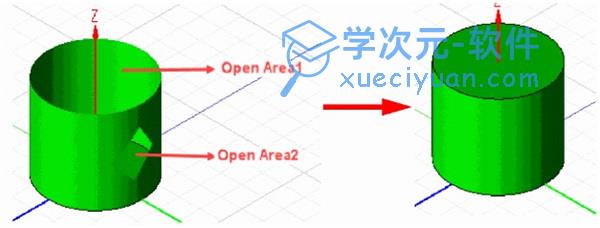

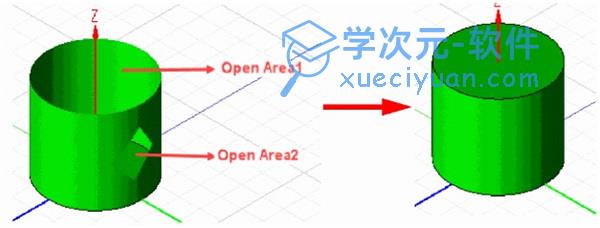

封面-您可以使用“建模器”菜单中的“模型清理-封面”选项来覆盖图纸主体的开放区域。

7、添加了用于多边形简化的新选项

(新)将SPD文件导入Clarity 3D Workbench时,导入的几何图形的质量可能不符合预期。 新选项“保守”已添加到“选项”对话框的“文件-转换器”部分,以改善多边形形状的处理。 选择保守选项时,导入的SPD文件中的形状处理较少。

配置需求

操作系统:Windows10(64位)、Windows 2012 Server(所有服务包)、Windows 2016 Server(所有服务包)。

注意:Windows 7不支持Clarity 3D Solver和Celsius with Hyper-V。

CPU:4核的IntelCorei7 4.30 GHz或AMD Ryzen7 4.30 GHz及以上。

RAM: 8GB RAM / 64GB RAM或更高。

空间:50GB空闲磁盘空间/ 500GB空闲磁盘空间。

建议主操作系统和仿真工作目录使用SSD硬盘。

显示器:1024 x 768显示分辨率真彩(16位彩色)/大显示器(或两个)全高清分辨率或更高。

显卡:专用显卡,1GB及以上显存。